# elmos"

E527.05

ROHS compliant

# Rain and Light Sensor with LIN SBC

PRODUCT PREVIEW - May 28, 2015

# **Features**

- Front end rain sensor amplifier

- · Four input channels for ambient light measurements

- High sensitivity.

- · Very high robustness against sun light

- Configurable µC window watchdog

- LIN Transceiver (V2.1, SAEJ2602, ISO9141)

- Two embedded LED Drivers, driving up to 40mA

- SPI Interface

- Temperature Sensor

- Extensive Diagnosis

- Few external components

- AEC-Q100 Qualification

# Applications

- · Optical rain sensing to control wiping systems

- Ambient light measurements to control

- Headlights

- Head-up Displays

- Air Conditioning

- Pollution Sensor

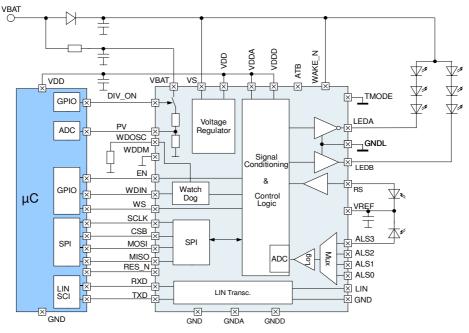

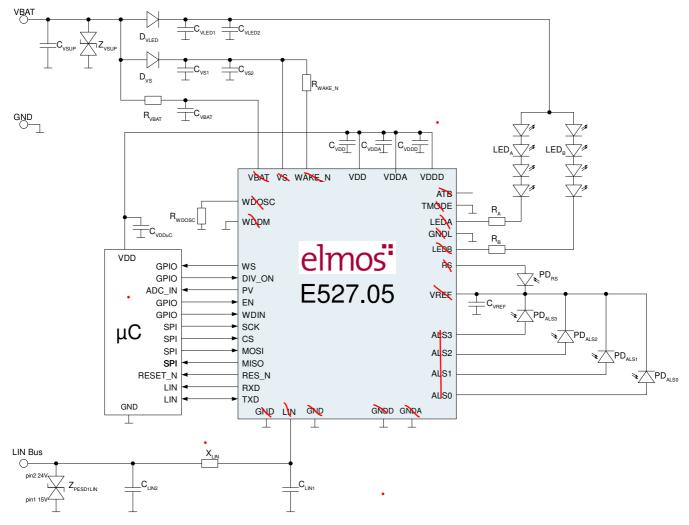

# **Typical Operating Circuit**

# **General Description**

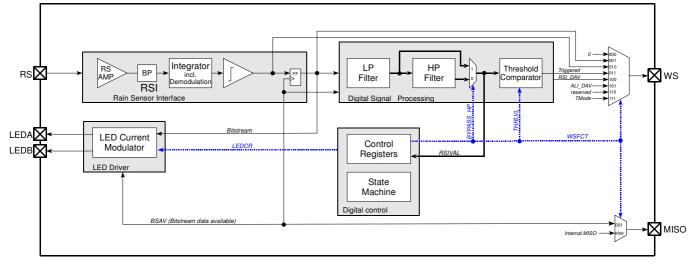

The RL IC (Rain and Light Sensor) is intended for controlling an optical sensor unit in automotive wiping systems. It provides two embedded LED drivers for stimuli generation. A special, high-sensitive receiver allows processing of a diode input signal without total reflection of the send signal, allowing reliable detection of rain. Due to the used HALIOS®-SD measurement method a very high robustness against sun light is provided. The device has four additional input channels for ambient light measurements.

# **Ordering Information**

| Ordering-No.: | Temp <sub>Junc</sub> Range | Package |

|---------------|----------------------------|---------|

| E52705A39B    | -40℃ to +105℃              | QFN44L7 |

PRODUCT PREVIEW - May 28, 2015

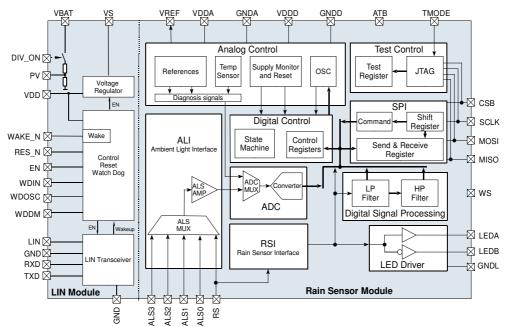

# **Functional Diagram**

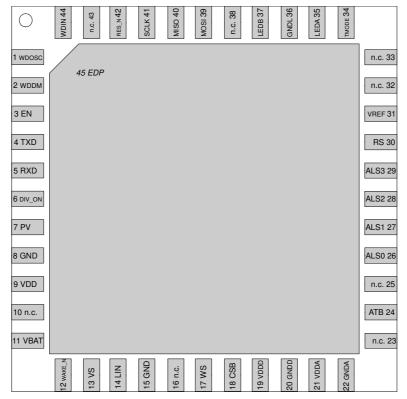

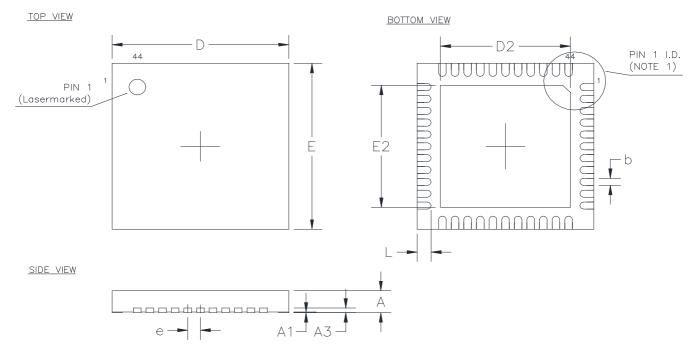

# Pin Configuration QFN44L7

PRODUCT PREVIEW - May 28, 2015

# Pin Description QFN44L7

| No | Name   | Туре      | Description                                                                                    |

|----|--------|-----------|------------------------------------------------------------------------------------------------|

| 1  | WDOSC  | A_I       | watchdog cycle time configuration                                                              |

| 2  | WDDM   | D I       | watchdog debug mode; internal pull down                                                        |

| 3  | EN     | <br>D I   | enable input; internal pull down                                                               |

| 4  | TXD    | D IO      | data transmit; internal pull up; open drain                                                    |

| 5  | RXD    | D_0       | receive data output; internal pull up; open drain                                              |

| 6  | DIV_ON | U         | Input to switch on the internal voltage divider; active high; internal pull down               |

| 7  | PV     | A O       | Voltage divider output                                                                         |

| 8  | GND    | S         | ground                                                                                         |

| 9  | VDD    | S         | 3.3V voltage regulator output                                                                  |

| 10 | n.c.   |           | not connected                                                                                  |

| 11 | VBAT   | HV_S      | Battery supply for the voltage divider                                                         |

| 12 | WAKE N | HV D I    | local wake up input; internal pull up to VS                                                    |

| 13 | <br>VS | HV S      | battery supply voltage                                                                         |

| 14 | LIN    | HV A IO   | LIN bus terminal                                                                               |

| 15 | GND    | S         | ground                                                                                         |

| 16 | n.c.   |           | not connected                                                                                  |

| 17 | WS     | AD IO     | Digital output pin; internal pull down if not configured as digital output or analog pin       |

|    | -      |           | (digital and analog test bus during test mode)                                                 |

| 18 | CSB    | D_I       | SPI chip select; low active; internal pull up                                                  |

|    |        |           | (JTAG pin TMS during test mode)                                                                |

| 19 | VDDD   | S         | Digital supply voltage                                                                         |

| 20 | GNDD   | S         | Digital ground                                                                                 |

| 21 | VDDA   | S         | Analog supply voltage                                                                          |

| 22 | GNDA   | S         | Analog ground                                                                                  |

| 23 | n.c.   |           | not connected                                                                                  |

| 24 | ATB    | A_IO      | not used; internal pull down (analog test bus during test mode)                                |

| 25 | n.c.   |           | not connected                                                                                  |

| 26 | ALS0   | A_I       | Ambient light input current 0;                                                                 |

| 07 | AL 04  | A 1       | Input for signal current of Ambient Light Sensor 0                                             |

| 27 | ALS1   | A_I       | Ambient light input current 1;<br>Input for signal current of Ambient Light Sensor 1           |

| 28 | ALS2   | A_I       | Ambient light input current 2;                                                                 |

| 20 | ALOL   | <u></u> i | Input for signal current of Ambient Light Sensor 2                                             |

| 29 | ALS3   | A_I       | Ambient light input current 3;                                                                 |

|    |        | -         | Input for signal current of Ambient Light Sensor 3                                             |

| 30 | RS     | A_I       | Rain sensor input current of receiver diode                                                    |

| 31 | VREF   | A_O       | Reference voltage to supply the sensor photo diodes                                            |

| 32 | n.c.   |           | not connected                                                                                  |

| 33 | n.c.   |           | not connected                                                                                  |

| 34 | TMODE  | D_I       | Test mode enable; active high; internal pull down; when low the JTAG and TMR are hold in reset |

| 35 | LEDA   | HV_A_O    | LED driver output; emitting path A                                                             |

| 36 | GNDL   | S         | LEDA/LEDB power ground                                                                         |

PRODUCT PREVIEW - May 28, 2015

| Name  | Туре                                                          | Description                                                                                         |

|-------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| LEDB  | HV_A_O                                                        | LED driver output; emitting path B                                                                  |

| n.c.  |                                                               | not connected                                                                                       |

| MOSI  | D_I                                                           | SPI serial data input; internal pull down; master out - slave in<br>(JTAG pin TDI during test mode) |

| MISO  | D_O                                                           | SPI serial data output; master in - slave out<br>(JTAG pin TDO during test mode)                    |

| SCLK  | D_I                                                           | SPI serial clock; internal pull down<br>(JTAG pin TCK during test mode)                             |

| RES_N | D_O                                                           | reset output; internal pull up; open drain                                                          |

| n.c.  |                                                               | not connected                                                                                       |

| WDIN  | D_I                                                           | watchdog trigger input; internal pull down                                                          |

| EDP   | S                                                             | Exposed die pad; has to be connected to large copper PCB ground plane for optimal heat dissipation. |

|       | LEDB<br>n.c.<br>MOSI<br>MISO<br>SCLK<br>RES_N<br>n.c.<br>WDIN | LEDB HV_A_O n.c. MOSI D_I MISO D_O SCLK D_I RES_N D_O n.c. WDIN D_I                                 |

Note: A = Analog, D = Digital, S = Supply, I = Input, O = Output, B = Bidirectional, HV = High Voltage

PRODUCT PREVIEW - May 28, 2015

# **1** Functional Safety

The development of this product is based on a process according to an ISO/TS 16949 certified quality management system. Functional safety requirements according to ISO 26262 have not been submitted to Elmos and therefore have not been considered for the development of this product.

# 2 Absolute Maximum Ratings

Table 2-1: Absolute Maximum Ratings

| No. | Description                                                             | Condition                                                                                                    | Symbol                                | Min  | Max                     | Unit |

|-----|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------|------|-------------------------|------|

| 1   | Supply voltages VDDA and VDDD                                           |                                                                                                              | V <sub>DDx,MAX</sub>                  | -0.3 | 3.6                     | V    |

| 2   | Voltage at pins related to VDDA:<br>ATB                                 |                                                                                                              | $V_{A,IO,MAX}$                        | -0.3 | VDDA+0.3<br>but <3.6    | V    |

| 3   | Voltage at pins related to VDDD:<br>SCLK, MISO, MOSI, CSB, WS           |                                                                                                              | $V_{\text{D},\text{IO},\text{MAX}}$   | -0.3 | VDDD+0.3<br>but <3.6    | V    |

| 4   | Voltage at pin VREF                                                     |                                                                                                              | $V_{REF,MAX}$                         | -0.3 | 3.6                     | V    |

| 5   | Voltage at pins related to VREF:<br>RS, ALS0 ,ALS1, ALS2, ALS3          |                                                                                                              | $V_{\text{REF},\text{IO},\text{MAX}}$ | -0.3 | VREF+0.3<br>but <3.6    | V    |

| 6   | Voltage at pin TMODE                                                    |                                                                                                              | $V_{\text{TMODE},\text{MAX}}$         | -0.3 | 3.6                     | V    |

| 7   | Voltage at pins LEDA and LEDB                                           |                                                                                                              | $V_{LEDx,MAX}$                        | -0.3 | 40                      | V    |

| 8   | Current into any ALS pin                                                |                                                                                                              | I <sub>ALSx,MAX</sub>                 | -    | 1.5                     | mA   |

| 9   | Current into pin RS                                                     |                                                                                                              | I <sub>RS,MAX</sub>                   | -    | 1.5                     | mA   |

| 10  | Power dissipation                                                       |                                                                                                              | P <sub>TOT</sub>                      | -    | tbd.                    | W    |

| 11  | Junction temperature                                                    |                                                                                                              | $T_{J,MAX}$                           | -40  | 150                     | °C   |

| 12  | Storage temperature                                                     |                                                                                                              | T <sub>STG</sub>                      | -40  | 125                     | °C   |

| 13  | DC voltage at pin VS, including load dump                               | continuous                                                                                                   | $V_{S,DC}$                            | -0.3 | 40                      | V    |

| 14  | DC voltage at pin WAKE_N                                                | continuous, 3.3kΩ pre-<br>resistor and 22nF<br>capacitance required,<br>33kΩ pull-up resistor<br>recommended | V <sub>WAKE_N,DC</sub>                | -2   | V <sub>S</sub> + 0.3    | V    |

| 15  | DC current at pin WAKE_N                                                | continuous                                                                                                   | I <sub>WAKE_N,DC</sub>                | -10  | 10                      | mA   |

| 16  | DC voltage at pin VDD                                                   | continuous                                                                                                   | V <sub>DD,DC3.3</sub>                 | -0.3 | 3.6                     | V    |

| 17  | DC current at pin VDD                                                   | continuous                                                                                                   |                                       | -130 | 1                       | mA   |

| 18  | DC input voltage at pin LIN, VBAT                                       | continuous                                                                                                   | $V_{\text{LIN,DC}}$                   | -24  | 40                      | V    |

| 19  | TRAN input voltage at pin LIN, VBAT                                     | pulse for max. 500ms                                                                                         | $V_{\text{LIN},\text{TRAN}}$          | -27  | 40                      | V    |

| 20  | DC Voltage Level for pin<br>EN,RES_N,RXD,TXD,WDIN,WDOSC,WDD<br>M,DIV_ON | continuous                                                                                                   | V <sub>IO,DC</sub>                    | -0.3 | V <sub>DD,DC</sub> +0.3 | V    |

| 21  | DC Current Level for pin<br>EN,RES_N,RXD,TXD,WDIN,WDOSC,WDD<br>M,DIV_ON | continuous                                                                                                   | I <sub>IO,DC</sub>                    | -10  | 1                       | mA   |

Stresses beyond these absolute maximum ratings listed below may cause permanent damage to the device. These are stress ratings only; operation of the device at these or any other conditions beyond those listed in the operational sections of this document is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. All voltages referred to VGND. Currents flowing into terminals are positive, those drawn out of a terminal are negative.

PRODUCT PREVIEW - May 28, 2015

# 3 ESD

Table 3-1: ESD Ratings Table

| Description                              | Condition                                             | Symbol                | Min  | Max  | Unit |

|------------------------------------------|-------------------------------------------------------|-----------------------|------|------|------|

| ESD HBM protection at pins LEDA,<br>LEDB | AEC-Q100-002<br>(HBM), C=100pF,<br>R=1.5kΩ chip level | $V_{ESD(HBM)}$        | -2   | +2   | kV   |

| ESD HBM protection at all other pins     | AEC-Q100-002<br>(HBM), C=100pF,<br>R=1.5kΩ chip level | $V_{ESD(HBM)}$        | -2   | +2   | kV   |

| ESD CDM protection at all pins           | AEC-Q100-011<br>(CDM), R=1Ω chip<br>level             | $V_{ESD(CDM)}$        | -500 | +500 | V    |

| ESD protection at pin LIN                | AEC-Q100-002<br>(HBM), C=100pF,<br>R=1.5kΩ chip level | VLIN,ESDHBM<br>to GND | -8   | +8   | kV   |

| ESD protection at pin LIN 1)             | IEC 61000-4-2<br>C=150 pF, R=330Ω                     | VLIN,ESD<br>to GND    | -8   | +8   | kV   |

1) verified with capacitor of CLIN=0pF, CLIN=220pF at pin LIN,CVS,RF=100nF at pin VS and CWAKE\_N=22nF, RWAKE\_N=3.3k $\Omega$  at pin WAKE\_N

# **4 Recommended Operating Conditions**

Table 4-1: Recommended Operating Conditions

| No. | Description                                                                | Condition               | Symbol                             | Min  | Тур | Max  | Unit |

|-----|----------------------------------------------------------------------------|-------------------------|------------------------------------|------|-----|------|------|

| 1   | Supply voltage pin VDDA                                                    |                         | V <sub>DDA</sub>                   | 3.1  | 3.3 | 3.5  | V    |

| 2   | Supply Voltage pin VDDD                                                    |                         | V <sub>DDD</sub>                   | 3.1  | 3.3 | 3.5  | V    |

| 3   | Difference between supply voltages VDDA and VDDD                           |                         |                                    | -0.3 | 0   | 0.3  | V    |

| 4   | Current into any ALS pin                                                   |                         | I <sub>ALSx</sub>                  | 1n   | -   | 1m   | А    |

| 5   | Current into pin RS                                                        |                         | I <sub>RS</sub>                    | 1n   | -   | 1m   | Α    |

| 6   | Ambient operating temperature                                              |                         | Т <sub>АМВ</sub>                   | -40  |     | +105 | °C   |

| 7   | DC voltage at pin VS                                                       |                         | $V_{s,FUNC}$                       | 5    | -   | 28   | V    |

| 8   | DC voltage at pin VS with limited functional range; no system reset occurs | $-60mA < I_{DD}$        | $V_{\text{S},\text{FL},\text{LR}}$ | 3.8  | -   | 7    | V    |

| 9   | DC voltage at pin VS with limited functional range; no system reset occurs | -60mA < I <sub>DD</sub> | $V_{\text{S},\text{FL},\text{HR}}$ | 18   | -   | 40   | V    |

| 10  | maximum IO current at each pin, if not spe-<br>cified otherwise            |                         | I <sub>IO,LUP</sub>                | -10  | -   | 10   | mA   |

This document contains information on a product under development. Elmos Semiconductor AG reserves the right to change or discontinue this product without notice.

PRODUCT PREVIEW - May 28, 2015

# **5 Electrical Characteristics**

$(V_{VDDx} = 3.1V \text{ to } 3.5V, T_{amb}=-40 \,^{\circ}\text{C} \text{ to } + 105 \,^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{VDDx}=3.3V \text{ and } T_{amb}=+25 \,^{\circ}\text{C}$ . Positive currents flow into the device pins.)

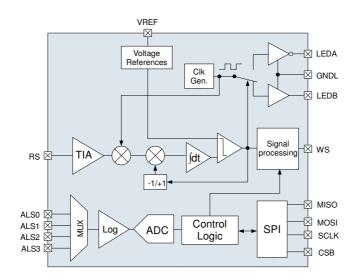

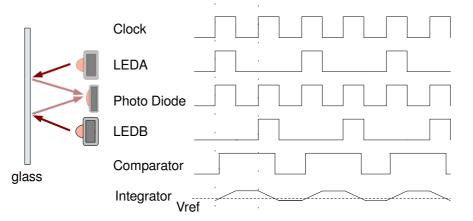

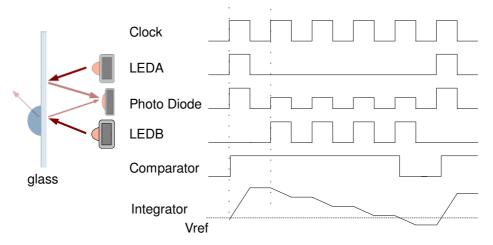

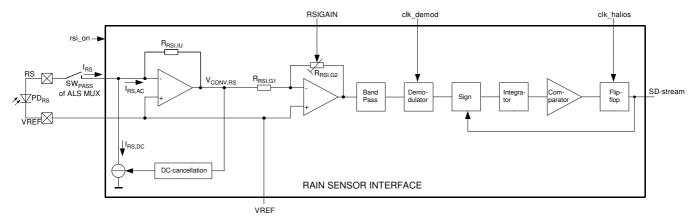

#### 5.1 Rain Sensor Module

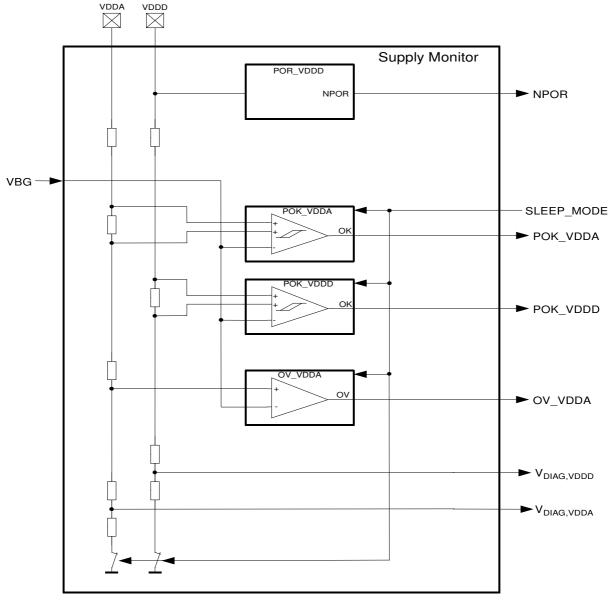

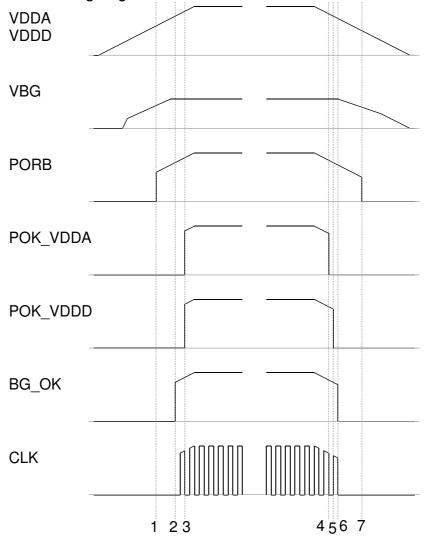

#### 5.1.1 Supply Monitor

Table 5.1.1-1: Electrical Parameters of Supply Monitor

| No. | Description                                                                                     | Condition                    | Symbol                                   | Min  | Тур  | Max  | Unit |

|-----|-------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------|------|------|------|------|

| 1   | VDDA voltage threshold to set<br>MON_C_VDDA comparator output from<br>low to high               | VDDA rising<br>edge          | $V_{\text{POK},\text{VDDA},\text{RISE}}$ | 2.75 | 2.9  | 3.05 | V    |

| 2   | VDDA voltage threshold to set<br>MON_C_VDDA comparator output from<br>high to low               | VDDA falling<br>edge         | $V_{POK,VDDA,FALL}$                      | 2.7  | 2.85 | 3.0  | V    |

| 3   | VDDD voltage threshold to set<br>MON_C_VDDD comparator output from<br>low to high <sup>1)</sup> | VDDD rising<br>edge          | $V_{\text{POK,VDDD,RISE}}$               | 2.60 | 2.8  | 3.0  | V    |

| 4   | VDDD voltage threshold to set<br>MON_C_VDDD comparator output from<br>high to low <sup>1)</sup> | VDDD falling<br>edge         | $V_{POK,VDDD,FALL}$                      | 2.5  | 2.67 | 2.85 | V    |

| 5   | VDDA overvoltage threshold                                                                      | VDDA rising and falling edge | V <sub>ov,vdda</sub>                     | 3.55 | 3.85 | 4.15 | V    |

<sup>1)</sup> measured with VDDA = VDDD ramp

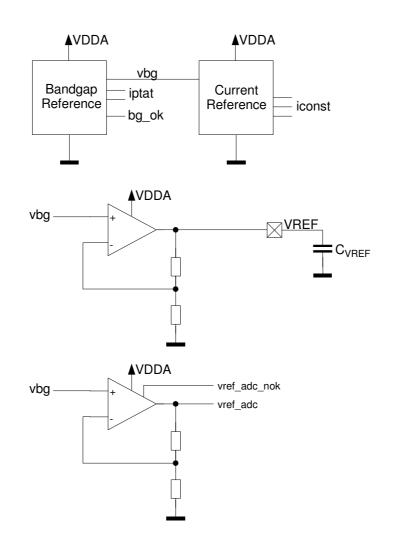

#### 5.1.2 References

Table 5.1.2-1: Electrical Parameters of References

| No. | Description                                           | Condition | Symbol                   | Min   | Тур   | Max   | Unit |

|-----|-------------------------------------------------------|-----------|--------------------------|-------|-------|-------|------|

| 1   | Internally generated reference voltage at<br>pin VREF |           | $V_{REF}$                | 1.288 | 1.388 | 1.488 | V    |

| 2   | Guaranteed current range supplied by pin VREF         |           | I <sub>VREF</sub>        | -3    | -     | 0.2   | mA   |

|     | Current into pin VREF in case of VREF shorted to GND  |           | I <sub>VREF,SC,GND</sub> | -25   | -16.3 | -     | mA   |

|     | Current into pin VREF in case of VREF shorted to VDDx |           | I <sub>VREF,SC,VDD</sub> | -     | 0.8   | 2     | mA   |

| 5   | Internally generated reference voltage for ADC        |           | $V_{REF,ADC}$            | 2.270 | 2.460 | 2.610 | V    |

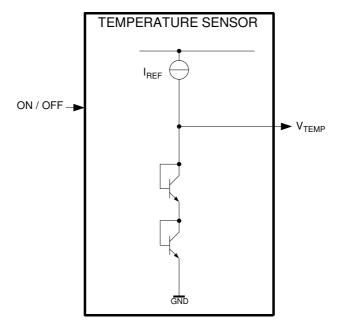

#### 5.1.3 Temperature Sensor

Table 5.1.3-1: Electrical Parameters of Temperature Sensor

| No. | Description                                                                                                                | Condition | Symbol               | Min | Тур            | Max | Unit |

|-----|----------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|-----|----------------|-----|------|

| 1   | Output voltage of temperature sensor at $25^\circ\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |           | $V_{\text{TEMP},25}$ | tbd | (1.24)<br>tbd. | tbd | V    |

|     | Slope of temperature sensor output voltage over absolute temperature <sup>*</sup> )                                        |           | SLOPEVTEMP           | tbd | -3.9           | tbd | mV/K |

<sup>\*)</sup> Not tested in production

PRODUCT PREVIEW - May 28, 2015

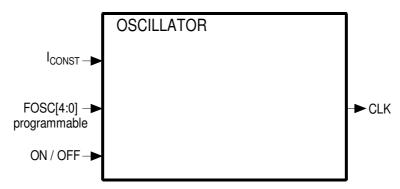

#### 5.1.4 Oscillator

Table 5.1.4-1: Electrical Parameters of Oscillator

| No. | Description                                          | Condition | Symbol                | Min | Тур | Max | Unit |

|-----|------------------------------------------------------|-----------|-----------------------|-----|-----|-----|------|

| 1   | Trimmed clk frequency                                |           | F <sub>CLK,TRIM</sub> | 7.2 | 8   | 8.8 | MHz  |

| 2   | Number of trimming positions for F <sub>CLK</sub> *) |           | N <sub>OSC,PROG</sub> | -   | 32  | -   |      |

| *)  | atad in production                                   |           |                       |     |     |     |      |

<sup>\*)</sup> Not tested in production

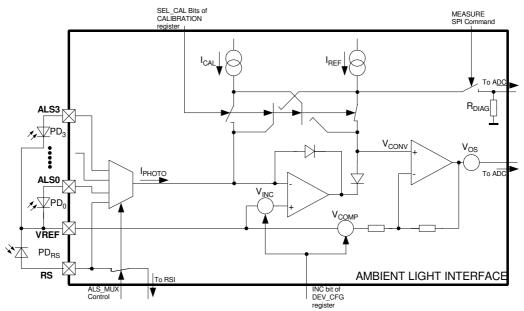

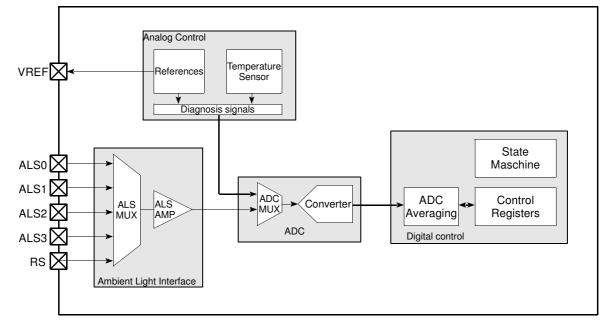

#### 5.1.5 Ambient Light Interface (ALI)

Table 5.1.5-1: Electrical Parameters of ALI

| No. | Description                                                                                                                                                        | Condition                                                         | Symbol                     | Min | Тур  | Max  | Unit |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------|-----|------|------|------|

| 1   | $\frac{I_{REF,ALI,HI}}{I_{CAL,ALI,HI}}$                                                                                                                            |                                                                   | Ratio <sub>н</sub>         |     | 4    |      | A/A  |

| 2   | $\frac{I_{REF,ALI,LO}}{I_{CAL,ALI,LO}}$                                                                                                                            |                                                                   | Ratio <sub>∟o</sub>        |     | 0.25 |      | A/A  |

| 3   | Valid input current for $I_{\text{REF,ALI,LO}}$ and $G_{\text{ALI,LO}}^{(1)}$                                                                                      | Iref=LO,<br>Gain=LO                                               | I <sub>PHOTO,ILO,GLO</sub> | 1n  |      | 300u | А    |

| 4   | Time to valid ADC value*)                                                                                                                                          | I <sub>РНОТО</sub> from<br>300uA to 1nA.<br>Leakage << 1nA.       | t <sub>ali,valid</sub>     |     |      | 13.1 | ms   |

| 5   | Time between measurement of two con-<br>secutive AUTOMODE ALS measure-<br>ments. <sup>*)</sup>                                                                     |                                                                   | t <sub>ali,autom</sub>     |     | 1    |      | ms   |

| 6   | Measured current at $I_{PHOTO}=1nA$ , Iref=LO,<br>Gain=LO, known temperature and $V_{ref}$ ,<br>without leakage and without further calibra-<br>tion <sup>°)</sup> | Iref=LO,<br>Gain=LO,<br>I <sub>РНОТО</sub> =1nA,<br>Temp < 125°   | I <sub>MEAS,1n</sub>       | 0.5 |      | 1.5  | nA   |

| 7   | Measured current at $I_{PHOTO}=1uA$ , Iref=LO, Gain=LO, known temperature and $V_{ref}$ and without further calibration                                            | Iref=LO,<br>Gain=LO,<br>I <sub>РНОТО</sub> =1uA,<br>Temp < 125°   | I <sub>MEAS,1u</sub>       | 0.7 |      | 1.5  | uA   |

| 8   | Measured current at I <sub>PHOTO</sub> =300uA, Iref=LO,<br>Gain=LO, known temperature and V <sub>ref</sub> and<br>without further calibration                      | Iref=LO,<br>Gain=LO,<br>I <sub>PHOTO</sub> =300uA,<br>Temp < 125° | I <sub>MEAS,300u</sub>     | 270 |      | 530  | uA   |

<sup>\*)</sup> Not tested in production

<sup>1)</sup> production test only with 10nA and 300uA

#### 5.1.6 Rain Sensor Interface (RSI)

Table 5.1.6-1: Electrical Parameters of RSI

| No. | Description                                                | Condition | Symbol                     | Min | Тур | Max | Unit |

|-----|------------------------------------------------------------|-----------|----------------------------|-----|-----|-----|------|

| 1   | Minimal adjustable gain of RSI <sup>1)</sup>               |           | G <sub>RSI,LO</sub>        | tbd | 100 | tbd | dBΩ  |

| 2   | Maximal adjustable gain of RSI                             |           | <b>G</b> <sub>RSI,HI</sub> | tbd | 142 | tbd | dBΩ  |

| 3   | Step width of RSI gain setting                             |           | G <sub>RSI,STEP</sub>      | tbd | 2.8 | tbd | dBΩ  |

| 4   | Number of trimming positions for gain of RSI <sup>*)</sup> |           | N <sub>GRSI</sub>          | -   | 16  | -   | -    |

PRODUCT PREVIEW - May 28, 2015

| No. | Description                                                        | Condition                  | Symbol                  | Min   | Тур   | Max   | Unit |

|-----|--------------------------------------------------------------------|----------------------------|-------------------------|-------|-------|-------|------|

| 5   | Modulator frequency of RSI <sup>*)</sup>                           | FREQ_SHIFT[2:<br>0] = b000 | $f_{\rm RSI,MOD}$       | 90    | 100   | 110   | kHz  |

|     | Modulator frequency of RSI with max. frequency shift <sup>*)</sup> | FREQ_SHIFT[2:<br>0] = b111 | f <sub>RSI,MOD,LO</sub> | 76.60 | 85.11 | 93.62 | kHz  |

| L   | Max. bandwidth of RSI*)                                            |                            | f <sub>RSI,BW</sub>     | 167   | -     | -     | Hz   |

<sup>\*)</sup> Not tested in production

<sup>1)</sup> DC current > 1uA

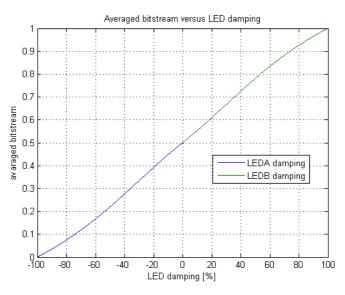

#### 5.1.7 LED Driver

Table 5.1.7-1: Electrical Parameters of LED Driver

| No. | Description                                         | Condition                                               | Symbol                  | Min | Тур           | Max            | Unit  |

|-----|-----------------------------------------------------|---------------------------------------------------------|-------------------------|-----|---------------|----------------|-------|

| 1   | output current range of pins LEDA and LEDB          |                                                         | I <sub>LEDx</sub>       |     |               | 40             | mA    |

| 2   | Current step size of pins LEDA and LEDB             |                                                         | I <sub>LEDx,STEP</sub>  |     | 2.5           |                | mA    |

| 3   | Number of trimming positions of ILEDx <sup>*)</sup> |                                                         | $N_{\text{LEDx,STEPS}}$ | -   | 16            | -              |       |

| 4   | Voltage at pins LEDA and LEDB <sup>*)</sup>         |                                                         | $V_{\text{LEDx}}$       | 0.8 |               | 18             | V     |

| 5   | Power dissipation at pin LEDA or LEDB <sup>*)</sup> | $P_{LEDx} = V_{LEDx} *$ $I_{LEDx}$                      | $P_{LEDx}$              |     |               | (0.54)<br>tbd. | W     |

| 6   | Current slew rate of pins LEDA and LEDB             | measured<br>between 20%<br>and 80% of I <sub>LEDx</sub> | I <sub>LEDx,SLEW</sub>  | tbd | tbd           | (90)<br>tbd    | mA/us |

|     | Current flowing into pins LEDx while driver is off  |                                                         | I <sub>LEDx,LOW</sub>   |     | (200)<br>tbd. |                | uA    |

\*) Not tested in production

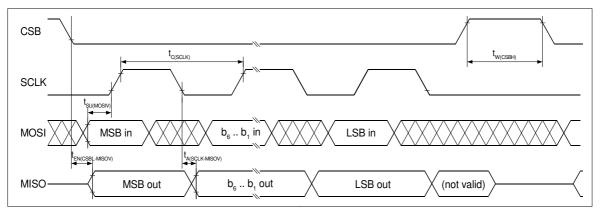

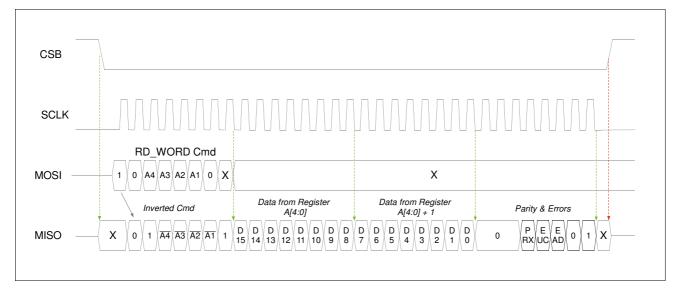

#### 5.1.8 Serial Peripheral Interface (SPI)

#### Table 5.1.8-1: Electrical Parameters of SPI

| No. | Description                                    | Condition                                | Symbol                       | Min | Тур | Max | Unit              |

|-----|------------------------------------------------|------------------------------------------|------------------------------|-----|-----|-----|-------------------|

| 1   | CSB, SCLK, MOSI input level low                |                                          | V <sub>IL(SPI)</sub>         |     |     | 0.3 | $V_{VDDD}$        |

| 2   | CSB, SCLK, MOSI input level high               |                                          | V <sub>IH(SPI)</sub>         | 0.7 |     |     | $V_{VDDD}$        |

| 3   | MISO output level low                          | $ I_{OL(SPI)}  < 2 \text{ mA}$           | V <sub>OL(SPI)</sub>         |     |     | 0.1 | $V_{\text{VDDD}}$ |

| 4   | MISO output level high                         | $ I_{OL(SPI)}  < 2 \text{ mA}$           | V <sub>OH(SPI)</sub>         | 0.9 |     |     | $V_{VDDD}$        |

| 5   | SPI clock frequency                            | $C_{\text{LOAD,MISO}} \leq 50 \text{pF}$ | $f_{SCLK} = 1 / t_{C(SCLK)}$ |     |     | 1   | MHz               |

| 6   | MOSI setup time <sup>*) 1)</sup>               |                                          | t <sub>SU(MOSIV)</sub>       | 20  |     |     | ns                |

| 7   | CSB to MISO time <sup>*) 1)</sup>              |                                          | t <sub>EN(CSBL-MISOV)</sub>  |     |     | 225 | ns                |

| 8   | SCLK to MISO time <sup>*) 1)</sup>             |                                          | $t_{A(\text{SCLK-MISOV})}$   |     |     | 80  | ns                |

| 9   | Time between two SPI frames <sup>*) 1)</sup>   |                                          | t <sub>w(CSBH)</sub>         | 1   |     |     | us                |

| 10  | Maximum allowed time between two SCLK edged.*) |                                          | t <sub>TO(SPI)</sub>         |     | 1   |     | ms                |

\*) Not tested in production

<sup>1)</sup> Also holds when the CSB pin is tied to zero.

PRODUCT PREVIEW - May 28, 2015

#### 5.2 LIN Module

#### 5.2.1 Power Supply and References; pin VS

Table 5.2.1-1: DC Characteristics

| No. | Description                                                                               | Condition                                                                                                                             | Symbol                   | Min | Тур | Max | Unit |

|-----|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-----|-----|------|

| 1   | current consumption in active mode                                                        | LIN dominant,<br>I <sub>DD</sub> =0mA                                                                                                 | I <sub>S,ACT,DOM</sub>   | -   | -   | 5   | mA   |

| 2   | current consumption in active mode                                                        | LIN recessive,<br>I <sub>DD</sub> =0mA                                                                                                | I <sub>S,ACT,REC</sub>   | -   | -   | 2   | mA   |

| 3   | standby current                                                                           | standby mode,<br>V <sub>S</sub> =V <sub>LIN</sub> =V <sub>WAKE_N</sub><br>=13.5V,<br>I <sub>DD</sub> =0mA,<br>T <sub>AMB</sub> <85 °C | I <sub>S,STBY</sub>      | -   | 70  | 98  | μΑ   |

| 4   | sleep current                                                                             | sleep mode,<br>LIN recessive,<br>$V_S = V_{LIN} = V_{WAKE_N}$<br>=13.5V                                                               | I <sub>S,SLEEP</sub>     | -   | 10  | 20  | μA   |

| 5   | sleep current, LIN is neither recessive nor dominant, not production tested <sup>*)</sup> | sleep mode,<br>LIN is floating<br>V <sub>S</sub> =V <sub>WAKE_N</sub><br>=13.5V, T <sub>AMP</sub> ><br>40 ℃                           | I <sub>S,SLEEP,LIN</sub> | -   | -   | 60  | μA   |

| 6   | sleep current                                                                             | sleep mode,<br>LIN is floating<br>$V_{s} = V_{WAKE_N}$<br>=13.5V, $V_{LIN} >$<br>$V_{LIN,THDOM}$                                      | I <sub>S,SLEEP,40C</sub> |     |     | 25  | μA   |

\*) Not tested in production

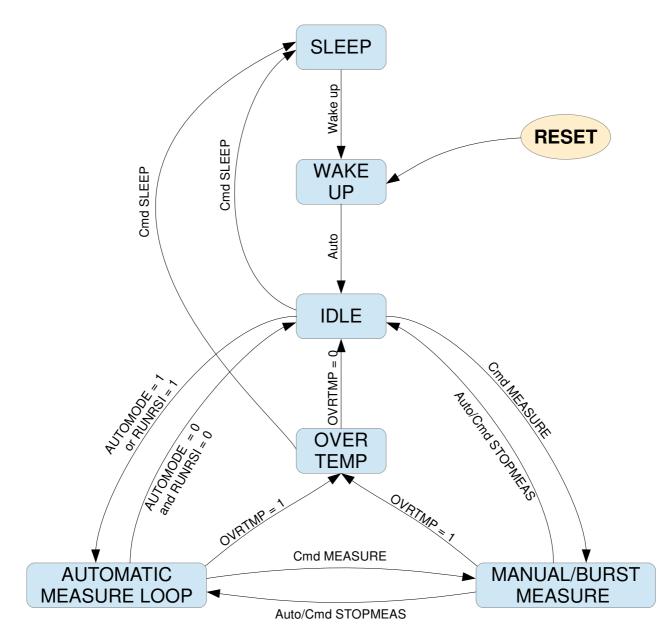

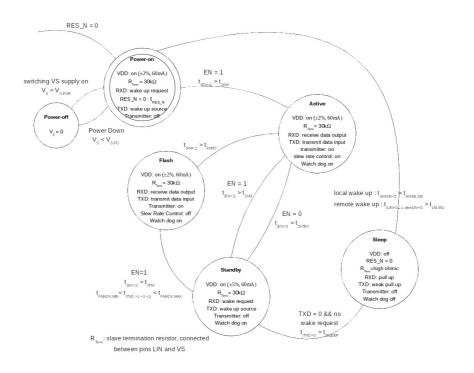

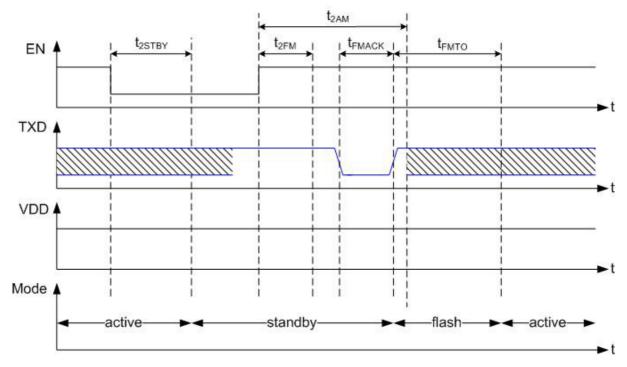

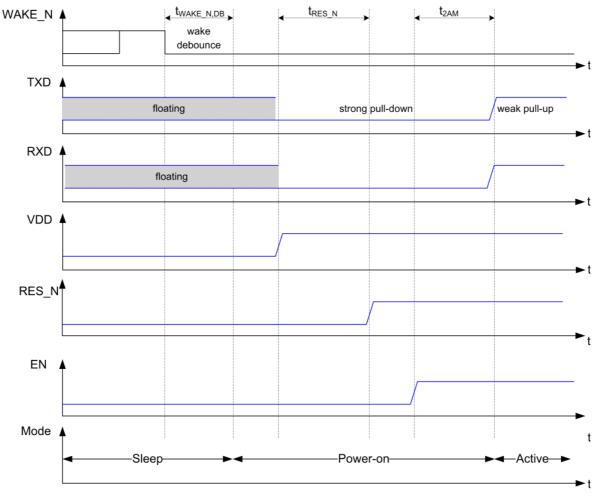

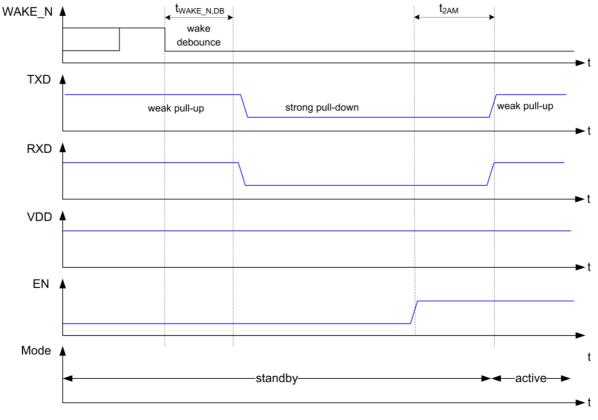

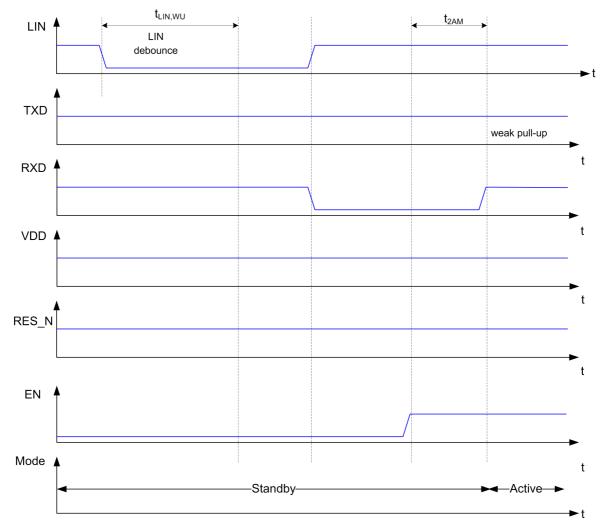

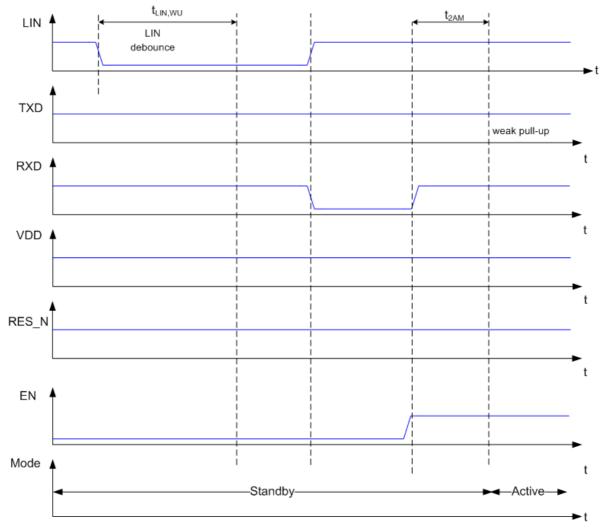

#### 5.2.2 LIN Module Operating Modes

Table 5.2.2-1: AC Characteristics

| No. | Description                                                         | Condition | Symbol                 | Min | Тур | Max | Unit |

|-----|---------------------------------------------------------------------|-----------|------------------------|-----|-----|-----|------|

| 1   | debounce filter for active mode transition                          |           | t <sub>2AM</sub>       | 23  | 25  | 44  | μs   |

| 2   | debounce filter for standby mode transition                         |           | t <sub>2STBY</sub>     | 23  | 25  | 44  | μs   |

| 3   | debounce filter for sleep mode transition                           |           | t <sub>2SLEEP</sub>    | 23  | 25  | 44  | μs   |

| 4   | debounce filter for flash mode transition                           |           | t <sub>2FM</sub>       | 2   | 4   | 6   | μs   |

| 5   | open window for flash mode acknowledge                              |           | t <sub>fmack</sub>     | 3   | -   | -   | μs   |

| 6   | flash mode time out                                                 |           | t <sub>FMTO</sub>      | 1.2 |     | 2   | ms   |

| 7   | delay for switching off the VDD regulator after entering sleep mode |           | t <sub>dd,offdel</sub> | 64  | 128 | -   | μs   |

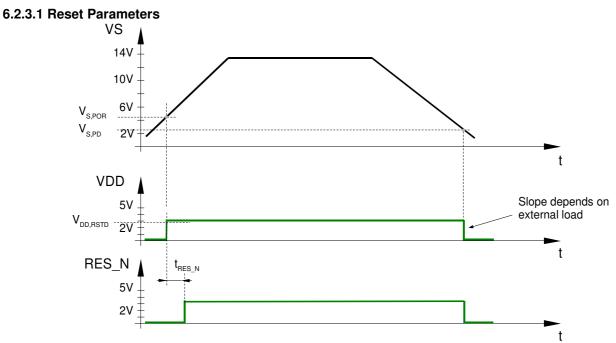

#### 5.2.3 Fail Safe System

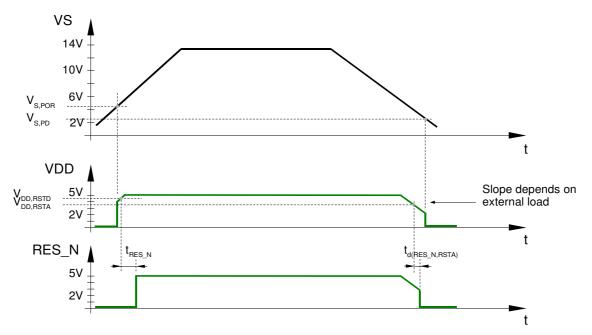

#### 5.2.3.1 Reset Parameters

Table 5.2.3.1-1: DC Characteristics Reset

| No. | Description                        | Condition | Symbol      | Min | Тур | Max | Unit |

|-----|------------------------------------|-----------|-------------|-----|-----|-----|------|

| 1   | power on reset according to pin VS |           | $V_{S,POR}$ | 4.0 | -   | 5.0 | V    |

PRODUCT PREVIEW - May 28, 2015

| No. | Description                                             | Condition                                            | Symbol                  | Min | Тур | Max | Unit |

|-----|---------------------------------------------------------|------------------------------------------------------|-------------------------|-----|-----|-----|------|

| 2   | power down threshold according to pin VS                |                                                      | $V_{S,PD}$              | 3.0 | -   | 3.8 | V    |

| 3   | reset assert level at pin VDD (3.3V device)             |                                                      | V <sub>DD,RSTA3.3</sub> | 2.4 | -   | 2.8 | V    |

| 4   | reset release level at pin <b>VDD</b> (3.3V device)     |                                                      | V <sub>DD,RSTD3.3</sub> | 2.6 | -   | 3.0 | V    |

| 5   | reset hysteresis at pin VDD (3.3V device) <sup>*)</sup> | V <sub>DD,RSTD3.3</sub> -<br>V <sub>DD,RSTA3.3</sub> | V <sub>DD,HYST3.3</sub> | 100 | -   | 400 | mV   |

\*) Not tested in production

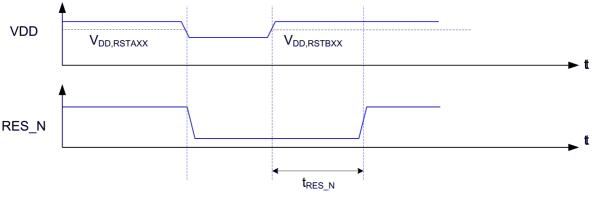

#### Table 5.2.3.1-2: AC Characteristic Reset

| No. | Description                      | Condition | Symbol                  | Min | Тур | Max | Unit |

|-----|----------------------------------|-----------|-------------------------|-----|-----|-----|------|

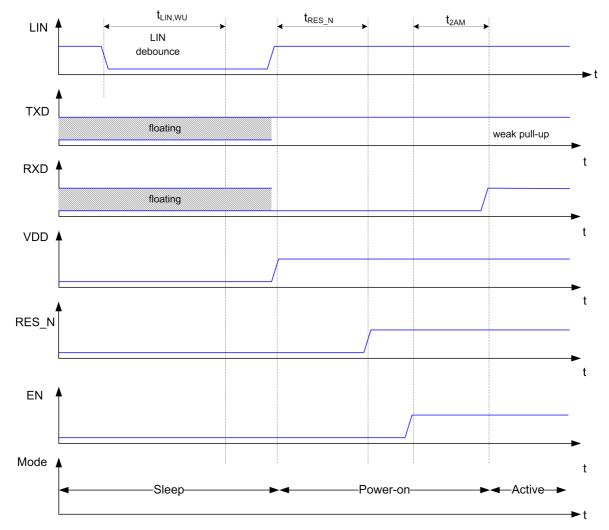

| 1   | pin <b>RES_N</b> activation time |           | t <sub>RES_N</sub>      | 2   | 3   | 5   | ms   |

| 2   | undervoltage debounce time       |           | t <sub>res_n,rsta</sub> | 60  |     | 90  | us   |

#### 5.2.3.2 Monitor Parameters

Table 5.2.3.2-1: DC Characteristics Monitoring

| No. | Description                                 | Condition                     | Symbol              | Min | Тур | Max | Unit |

|-----|---------------------------------------------|-------------------------------|---------------------|-----|-----|-----|------|

| 1   | thermal shutdown flag threshold             |                               | T <sub>SHDN</sub>   | 150 | -   | 180 | °C   |

| 2   | thermal shutdown flag hysteresis. $^{*)}$   |                               | T <sub>HYST</sub>   | 5   | -   | 22  | K    |

| 3   | LIN overvoltage condition in dominant state | active mode,<br><b>TXD</b> =0 | $V_{\text{LIN,OV}}$ | -   | 4   | -   | V    |

\*) Not tested in production

#### Table 5.2.3.2-2: AC Characteristics Monitoring

| No. | Description                               | Condition    | Symbol               | Min | Тур | Max | Unit |

|-----|-------------------------------------------|--------------|----------------------|-----|-----|-----|------|

| 1   | LIN over voltage debounce time            | LIN dominant | t <sub>LIN,OV</sub>  | -   | 25  | -   | μs   |

| 2   | voltage regulator shut down debounce time |              | t <sub>DD,SHDN</sub> | -   | 50  | -   | μs   |

#### 5.2.4 Wake Up

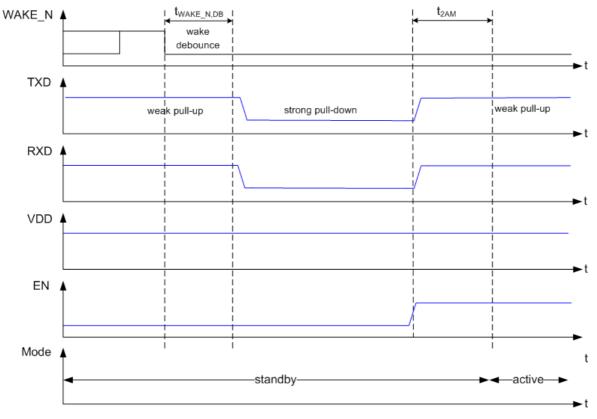

#### 5.2.4.1 Local Wake Up; pin WAKE\_N

Table 5.2.4.1-1: DC Characteristics

| No. | Description                    | Condition                | Symbol                   | Min | Тур | Max | Unit |

|-----|--------------------------------|--------------------------|--------------------------|-----|-----|-----|------|

| 1   | leakage current                | $V_{WAKE_N} = V_S = 18V$ | I <sub>WAKE_N,LEAK</sub> | -5  | -   | 5   | μA   |

| 2   | input low level                |                          | $V_{WAKE_N,INL}$         | 2.5 | 3.0 | 3.5 | V    |

| 3   | input high level               |                          | $V_{WAKE_N,INH}$         | 3.0 | 3.5 | 4.0 | V    |

| 4   | input hysteresis <sup>*)</sup> |                          | $V_{WAKE_N,HYST}$        | 0.2 | 0.5 | 0.8 | V    |

| 5   | pull up current                | V <sub>s</sub> < 28 V,   | WAKE_N,PU                | -30 | -10 | -   | μA   |

|     |                                | $V_{WAKE_N} = 0 V$       |                          |     |     |     |      |

\*) Not tested in production

#### Table 5.2.4.1-2: AC Characteristics

| No. | Description                  | Condition | Symbol                 | Min | Тур | Max | Unit |

|-----|------------------------------|-----------|------------------------|-----|-----|-----|------|

| 1   | input debouncing filter time |           | t <sub>wake_n,db</sub> | -   | -   | 25  | μs   |

PRODUCT PREVIEW - May 28, 2015

#### 5.2.5 Voltage Regulator; pin VDD

#### Table 5.2.5-1: DC Characteristics Active Mode

| No. | Description                                    | Condition   | Symbol                 | Min  | Тур | Max  | Unit |

|-----|------------------------------------------------|-------------|------------------------|------|-----|------|------|

| 1   | output voltage range                           | active mode | V <sub>DD,ACT3.3</sub> | 3.23 | 3.3 | 3.37 | V    |

| 2   | output current range with 2% VDD accur-<br>acy |             | I <sub>DD,ACT60</sub>  | -60  | -   | -    | mA   |

| 3   | output current range with 5% VDD accur-<br>acy |             | I <sub>DD,ACT100</sub> | -100 | -   | -    | mA   |

| 4   | output current limitation                      |             | I <sub>DD,LIM</sub>    | -230 | -   | -130 | mA   |

| 5   | Power supply ripple<br>rejection <sup>*)</sup> |             | PSRR                   | 50   |     |      | dB   |

<sup>\*)</sup> Not tested in production

#### Table 5.2.5-2: DC Characteristics Standby Mode

| No.                                   | Description            | Condition    | Symbol           | Min   | Тур | Max   | Unit |  |

|---------------------------------------|------------------------|--------------|------------------|-------|-----|-------|------|--|

| 1                                     | output voltage range*) | standby mode | $V_{DD,STBY3.3}$ | 3.135 | 3.3 | 3.465 | V    |  |

| <sup>1</sup> Not tested in production |                        |              |                  |       |     |       |      |  |

Not tested in production

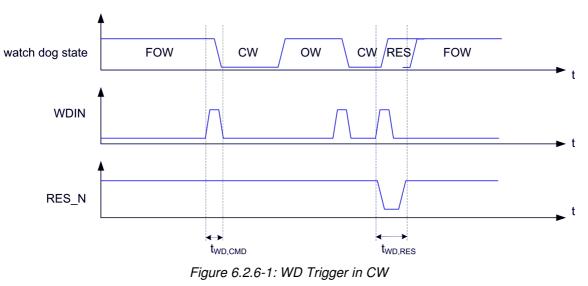

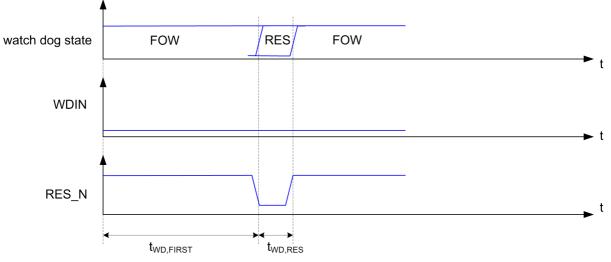

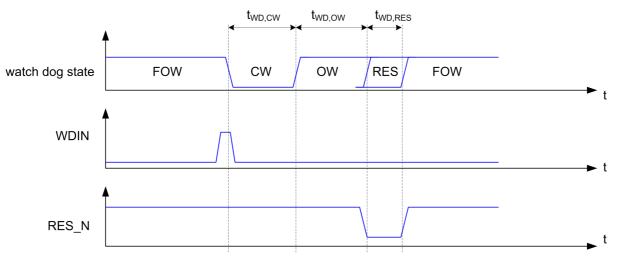

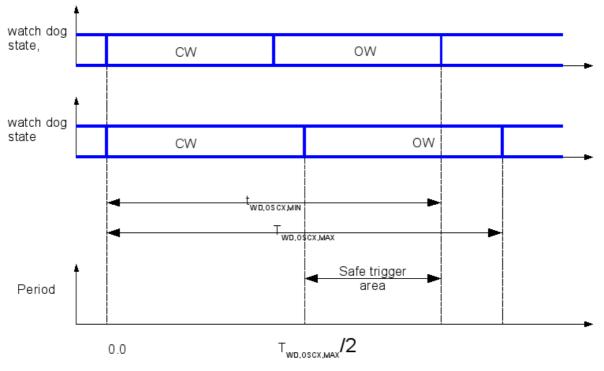

#### 5.2.6 Watchdog

Table 5.2.6-1: AC Characteristics

| No. | Description                                 | Condition                                        | Symbol                  | Min  | Тур | Max   | Unit |

|-----|---------------------------------------------|--------------------------------------------------|-------------------------|------|-----|-------|------|

| 1   | watchdog period for $10k\Omega$ resistance  | $R_{WDOSC}=10k\Omega$                            | twD,OSC10k              | 7.2  | 10  | 13.2  | ms   |

| 2   | watchdog period for $100k\Omega$ resistance | $R_{WDOSC}=100k\Omega$                           | t <sub>WD,OSC100k</sub> | 88.2 | 100 | 112.2 | ms   |

| 3   | first trigger open window                   | open window<br>after <b>RES_N</b> is<br>released | t <sub>wd,FIRST</sub>   | 91   | 110 | 135   | ms   |

| 4   | open window duty                            |                                                  | d <sub>wD,OW</sub>      | -    | 50  | -     | %    |

| 5   | closed window duty                          |                                                  | d <sub>wD,CW</sub>      | -    | 50  | -     | %    |

| 6   | watchdog reset time                         |                                                  | t <sub>wD,RES</sub>     | 414  | 512 | 645   | μS   |

| 7   | trigger command pulse width                 |                                                  | t <sub>wD,CMD</sub>     | 8    | -   | -     | μs   |

#### 5.2.7 LIN Transceiver; pin LIN

Table 5.2.7-1: DC characteristics

| No. | Description                      | Condition                                                                                                                                                         | Symbol                       | Min                | Тур | Max | Unit           |

|-----|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------|-----|-----|----------------|

| 1   | functional range LIN transceiver |                                                                                                                                                                   | $V_{\text{LIN,VS}}$          | 7                  | -   | 18  | V              |

| 2   | recessive output voltage         | TXD=1                                                                                                                                                             | $V_{\text{LIN,REC}}$         | $V_{\text{S}}$ -1V | -   | Vs  | -              |

| 3   | dominant output voltage          | $\begin{array}{l} \textbf{TXD}=0,\\ \textbf{V}_{\text{S}}=7.0\text{V},\\ \textbf{R}_{\text{LIN}}=0.5\text{k}\Omega \text{ to } \textbf{V}_{\text{S}} \end{array}$ | V <sub>LIN,DOM</sub>         | -                  | -   | 1.2 | V              |

| 4   | dominant output voltage          | $\begin{array}{l} \textbf{TXD}=0, \ V_{\text{S}}=18\text{V}, \\ \textbf{R}_{\text{LIN}}=0.5\text{k}\Omega \ \text{to} \ V_{\text{S}} \end{array}$                 | $V_{\text{LIN},\text{DOM1}}$ | -                  | -   | 2.0 | V              |

| 5   | receiver dominant level          |                                                                                                                                                                   | $V_{\text{LIN,THDOM}}$       | -                  | -   | 0.4 | Vs             |

| 6   | receiver recessive level         |                                                                                                                                                                   | $V_{\text{LIN,THREC}}$       | 0.6                | -   | -   | $V_{\text{S}}$ |

PRODUCT PREVIEW - May 28, 2015

| No. | Description                                               | Condition                                                                                 | Symbol                      | Min   | Тур | Max   | Unit |

|-----|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------|-------|-----|-------|------|

| 7   | LIN bus center voltage                                    | $V_{\text{LIN,BUSCNT}} = (V_{\text{LIN,THDOM}} + V_{\text{LIN,TH}})/2$                    | VLIN,BUSCNT                 | 0.475 | -   | 0.525 | Vs   |

| 8   | receiver hysteresis                                       | V <sub>LIN,THREC</sub> -<br>V <sub>LIN,THDOM</sub>                                        | $V_{\text{LIN},\text{HYS}}$ | -     | -   | 0.175 | Vs   |

| 9   | output current limitation                                 | $V_{LIN} = V_{VS,MAX} =$<br>18 V                                                          | I <sub>LIN,LIM</sub>        | 40    | -   | 200   | mA   |

| 10  | pull up resistance                                        |                                                                                           | <b>R</b> LIN,SLAVE          | 20    | 33  | 60    | kΩ   |

| 11  | leakage current flowing into pin LIN                      | transmitter pass-<br>ive, $7V < V_S < 18V$ ,<br>$7V < V_{LIN} < 18V$ ,<br>$V_{LIN} > V_S$ | I <sub>LIN,BUSREC</sub>     | -     | 8   | 20    | μA   |

| 12  | pull up current flowing out of pin LIN                    | transmitter pass-<br>ive, 7V <v<sub>S&lt;18V,<br/>V<sub>LIN</sub>=0V</v<sub>              | I <sub>LIN,BUSDOM</sub>     | -1    | -   | -     | mA   |

| 13  | leakage current, ground disconnected<br>(GND device = VS) | V <sub>S</sub> =13.5V,<br>0V <v<sub>LIN&lt;18V</v<sub>                                    | I <sub>LIN,NOGND</sub>      | -1    | -   | 0.1   | mA   |

| 14  | leakage current, supply disconnected                      | V <sub>S</sub> =0V,<br>0V <v<sub>LIN&lt;18V</v<sub>                                       | I <sub>LIN</sub>            | -     | 8   | 20    | μA   |

| 15  | leakage current, supply disconnected, T = 85 °C           | V <sub>S</sub> =0V,<br>0V <v<sub>LIN&lt;18V</v<sub>                                       | I <sub>LIN,85</sub>         | -     | -   | 15    | μA   |

| 16  | clamping voltage <sup>*)</sup>                            | V <sub>S</sub> =0V, I <sub>LIN</sub> =1mA                                                 | V <sub>LIN,CLAMP</sub>      | 40    |     | _     | V    |

-

#### Table 5.2.7-2: AC characteristics

| No. | Description                                     | Condition                                                                                                                                                                       | Symbol                      | Min | Тур | Max | Unit |

|-----|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|-----|-----|------|

| 1   | input capacitance <sup>*)</sup>                 | $7V < V_{s} < 18V$                                                                                                                                                              | $C_{\text{LIN},\text{PIN}}$ | -   | -   | 30  | рF   |

| 2   | output slew rate                                | $\begin{array}{l} C_{\text{LIN}}{=}1{-}10nF,\\ R_{\text{LIN}}{=}0.5{-}1k\Omega,\\ 1\mu s{-}t_{\text{LIN}}{<}5\mu s,\\ V_{\text{S}}{=}18V \end{array}$                           | SR <sub>LIN,OUT</sub>       | 1   | -   | 3   | V/µs |

| 3   | output slew rate                                | $\begin{array}{l} C_{\text{LIN}} = 1\text{-}10nF, \\ R_{\text{LIN}} = 0.5\text{-}1k\Omega, \\ 1\mu\text{s} < t_{\text{LIN}} < 5\mu\text{s}, \\ V_{\text{S}} = 7.0V \end{array}$ | SR <sub>LIN,OUT1</sub>      | 0.5 | -   | 3   | V/µs |

| 4   | symmetry of rising and falling edge             | V <sub>S</sub> =18V                                                                                                                                                             | t <sub>lin,sym</sub>        | -5  | -   | 5   | μS   |

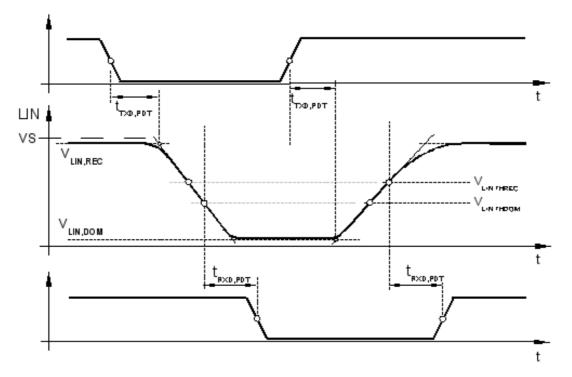

| 5   | transmit propagation delay, is deleted          |                                                                                                                                                                                 | t <sub>txd,pdt</sub>        | -   | -   | 4   | μS   |

| 6   | transmit propagation delay symmetry, is deleted |                                                                                                                                                                                 | t <sub>txd,sym</sub>        | -2  | -   | 2   | μS   |

| 7   | receive propagation delay                       |                                                                                                                                                                                 | t <sub>RXD,PDR</sub>        | -   | -   | 6   | μS   |

| 8   | receive propagation delay symmetry              |                                                                                                                                                                                 | t <sub>RXD,SYM</sub>        | -2  | -   | 2   | μS   |

| 9   | LIN bus pulse receiver debounce time            |                                                                                                                                                                                 | t <sub>LIN,DB</sub>         | 0.3 | -   | 6   | μS   |

| 10  | wake-up debounce time                           |                                                                                                                                                                                 | t <sub>lin,wu</sub>         | 70  | -   | 150 | μS   |

PRODUCT PREVIEW - May 28, 2015

| No. | Description                | Condition                                                                                                                                                                                                                                                                                                     | Symbol               | Min   | Тур | Max   | Unit |

|-----|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-----|-------|------|

| 11  | Duty cycle 1 <sup>1)</sup> | $\begin{array}{l} V_{\text{LIN,THREC}}(max)\\ = 0.744^*V_{\text{S}},\\ V_{\text{LIN,THDOM}}(max)\\ = 0.581^*V_{\text{S}}, V_{\text{S}}{=}7{-}\\ 18V, t_{\text{BIT}}{=}50\mu\text{s},\\ D_{\text{LIN,1}}{=}t_{\text{BUSREC}}(min)/\\ (2^*t_{\text{BIT}}) \end{array}$                                          | D <sub>LIN,1</sub>   | 0.396 | -   | -     | -    |

| 12  | Duty cycle 2 <sup>1)</sup> | $\begin{array}{l} V_{\text{LIN,THREC}}(min)\\ = 0.422^{*}V_{\text{S}},\\ V_{\text{LIN,THDOM}}(min)\\ = 0.284^{*}V_{\text{S}}, V_{\text{S}}{=}7{-}\\ 18V, t_{\text{BIT}}{=}50\mu\text{s},\\ D_{\text{LIN,2}}{=}t_{\text{BUSREC}}(max)/\\ (2^{*}t_{\text{BIT}}) \end{array}$                                    | D <sub>LIN,2</sub>   | -     | -   | 0.581 | -    |

| 13  | Duty cycle 3 <sup>1)</sup> | $\begin{array}{l} V_{,\text{LIN,THREC}}(\text{max}) \\ = 0.778^{*}V_{\text{S}}, \\ V_{\text{LIN,THDOM}}(\text{max}) \\ = 0.616^{*}V_{\text{S}}, V_{\text{S}} = 7 \text{-} \\ 18V, t_{\text{BIT}} = 96\mu\text{s}, \\ D_{\text{LIN,3}} = t_{\text{BUSREC}}(\text{min}) / \\ (2^{*}t_{\text{BIT}}) \end{array}$ | D <sub>LIN,3</sub>   | 0.417 | -   | -     | -    |

| 14  | Duty cycle 4 <sup>1)</sup> | $\begin{array}{l} V_{\text{LIN,THREC}}(\text{min}) \\ = 0.389^{*}V_{\text{S}}, \\ V_{\text{LIN,THDOM}}(\text{min}) \\ = 0.251^{*}V_{\text{S}}, V_{\text{S}} = 7 - \\ 18V, t_{\text{BIT}} = 96\mu\text{s}, \\ D_{\text{LIN,4}} = t_{\text{BUSREC}}(\text{max}) / \\ (2^{*}t_{\text{BIT}}) \end{array}$         | D <sub>LIN,4</sub>   | -     | -   | 0.590 | -    |

| 15  | receive data baud rate     | flash mode,<br>V <sub>s</sub> =13V                                                                                                                                                                                                                                                                            | B <sub>LIN,RXD</sub> |       |     | 250   | kBds |

| 16  | transmit data baud rate    | flash mode,<br>V <sub>s</sub> =13V                                                                                                                                                                                                                                                                            | BLIN,TXD             |       |     | 115   | kBds |

\*) Not tested in production

1) Bus load conditions (C\_{LIN},R\_{LIN}): 1nF, 1k\Omega/6.8nF, 660\Omega/10nF, 500\Omega

#### 5.2.8 IO Peripherals

#### 5.2.8.1 Enable; pin EN

Table 5.2.8.1-1: DC Characteristics

| No. | Description            | Condition           | Symbol               | Min  | Тур | Max  | Unit            |

|-----|------------------------|---------------------|----------------------|------|-----|------|-----------------|

| 1   | input low level range  |                     | $V_{\text{EN,INL}}$  | 0    | -   | 0.25 | $V_{\text{DD}}$ |

| 2   | input high level range |                     | $V_{\text{EN,INH}}$  | 0.75 |     | 1.0  | $V_{\text{DD}}$ |

| 3   | pull down resistor     | $V_{EN}=5.0V$       | $R_{EN,PD}$          | 80   |     | 220  | kΩ              |

| 4   | input leakage          | V <sub>EN</sub> =0V | I <sub>EN,LEAK</sub> | -5   | -   | 5    | μA              |

PRODUCT PREVIEW - May 28, 2015

#### 5.2.8.2 Transmit Data Input; pin TXD

Table 5.2.8.2-1: DC Characteristics

| No. | Description              | Condition             | Symbol               | Min  | Тур | Max  | Unit            |

|-----|--------------------------|-----------------------|----------------------|------|-----|------|-----------------|

| 1   | input low voltage range  |                       | $V_{\text{TXD,INL}}$ | 0    | -   | 0.25 | $V_{\text{DD}}$ |

| 2   | input high voltage range |                       | $V_{\text{TXD,INH}}$ | 0.75 | -   | 1.0  | $V_{\text{DD}}$ |

| 3   | output low level range   | I <sub>TXD</sub> =1mA | V <sub>TXD,OUT</sub> | -0.3 | -   | 0.6  | V               |

| 4   | TXD pull up resistor     | V <sub>TXD</sub> =0V  | R <sub>TXD,PU</sub>  | 80   |     | 220  | kΩ              |

#### Table 5.2.8.2-2: AC Characteristics

| No. | Description               | Condition       | Symbol              | Min | Тур | Max | Unit |

|-----|---------------------------|-----------------|---------------------|-----|-----|-----|------|

| 1   | time out detection of TXD | TXD = 0 V, act- | t <sub>txd,to</sub> | 6   | 10  | 14  | ms   |

|     |                           | ive mode        |                     |     |     |     |      |

#### 5.2.8.3 Receive Data Output; pin RXD

Table 5.2.8.3-1: DC Characteristics

| No. | Description            | Condition             | Symbol        | Min  | Тур | Max | Unit |

|-----|------------------------|-----------------------|---------------|------|-----|-----|------|

| 1   | output low level range | I <sub>RXD</sub> =1mA | $V_{RXD,OUT}$ | -0.3 | -   | 0.6 | V    |

| 2   | pull up resistance     | V <sub>RXD</sub> =0V  | $V_{RXD,PU}$  | 3    | 5   | 10  | kΩ   |

#### 5.2.8.4 Reset; pin RES\_N

Table 5.2.8.4-1: DC Characteristics

| No. | Description            | Condition               | Symbol                        | Min  | Тур | Max | Unit |

|-----|------------------------|-------------------------|-------------------------------|------|-----|-----|------|

| 1   | output low level range | I <sub>RES_N</sub> =1mA | $V_{\text{RES}_N,\text{OUT}}$ | -0.3 | -   | 0.6 | V    |

| 2   | pull up resistance     | $V_{\text{RES}_N}=0V$   | I <sub>RES_N,PU</sub>         | 3    | 5   | 10  | kΩ   |

#### 5.2.8.5 Watchdog Trigger Input; pin WDIN

Table 5.2.8.5-1: DC Characteristics

| No. | Description            | Condition | Symbol                | Min  | Тур | Max  | Unit            |

|-----|------------------------|-----------|-----------------------|------|-----|------|-----------------|

| 1   | input low level range  |           | $V_{WDIN\_INL}$       | 0    | -   | 0.25 | $V_{\text{DD}}$ |

| 2   | input high level range |           | V <sub>WDIN,INH</sub> | 0.75 | -   | 1.0  | $V_{\text{DD}}$ |

#### 5.2.8.6 Watchdog Cycle Time Configuration; pin WDOSC

Table 5.2.8.6-1: DC Characteristics

| No. | Description       | Condition         | Symbol                 | Min | Тур | Max | Unit |

|-----|-------------------|-------------------|------------------------|-----|-----|-----|------|

| 1   | reference current | $V_{WDOSC} = 1 V$ | I <sub>WDOSC,REF</sub> | -   | 14  | -   | μA   |

#### 5.2.8.7 Watchdog Debug Mode; pin WDDM

Table 5.2.8.7-1: DC Characteristics

| No. | Description            | Condition | Symbol    | Min  | Тур | Max  | Unit            |

|-----|------------------------|-----------|-----------|------|-----|------|-----------------|

| 1   | input low level range  |           |           | 0    | -   | 0.25 | $V_{\text{DD}}$ |

| 2   | input high level range |           | Vwddm,inh | 0.75 | -   | 1.0  | $V_{\text{DD}}$ |

This document contains information on a product under development. Elmos Semiconductor AG reserves the right to change or discontinue this product without notice.

PRODUCT PREVIEW - May 28, 2015

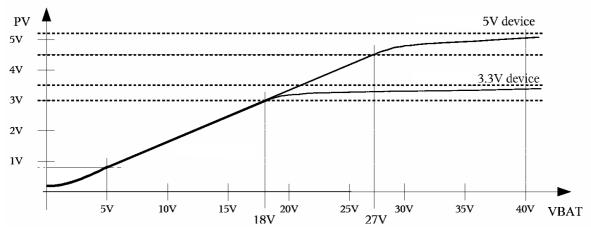

#### 5.2.9 VBAT Voltage divider

#### Table 5.2.9-1: DC Characteristics

| livid ex vetie                    |                                                                                                                                                    |                                                                                                                                                                                                                                                          | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Max  | Unit                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| livider ratio                     | $V_{s,PD} < V_S < 18 V$                                                                                                                            | DR <sub>PV,3.3V</sub>                                                                                                                                                                                                                                    | 5.86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6.04 |                                                                                                                                                                                                                                                                                                                                                           |